Technischer Support und Kundendienst

FR4-Leiterplattenprototyp

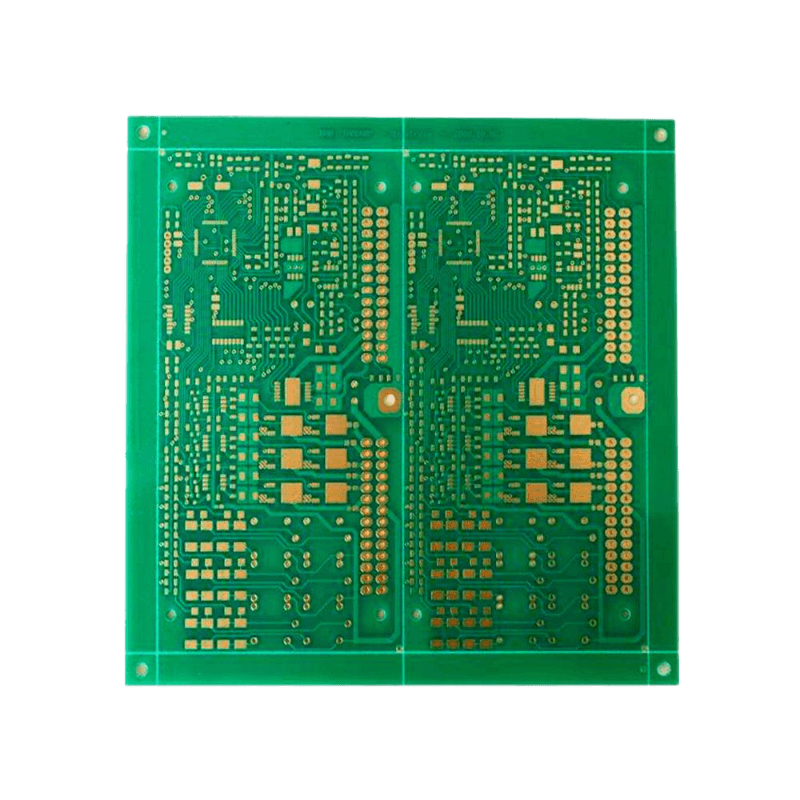

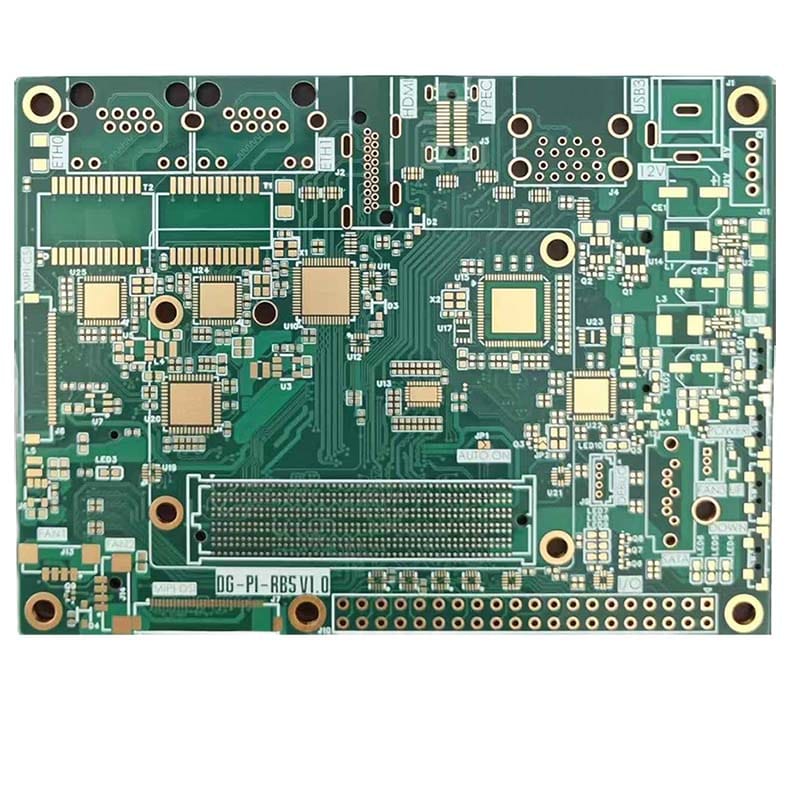

Mehrschichtige Leiterplatte

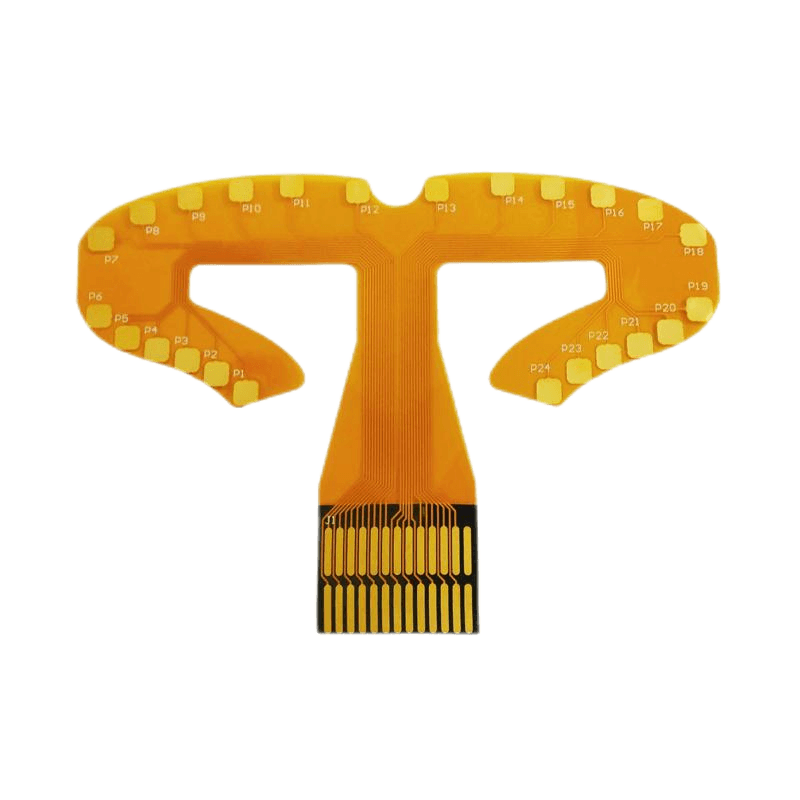

Flexible Leiterplatte

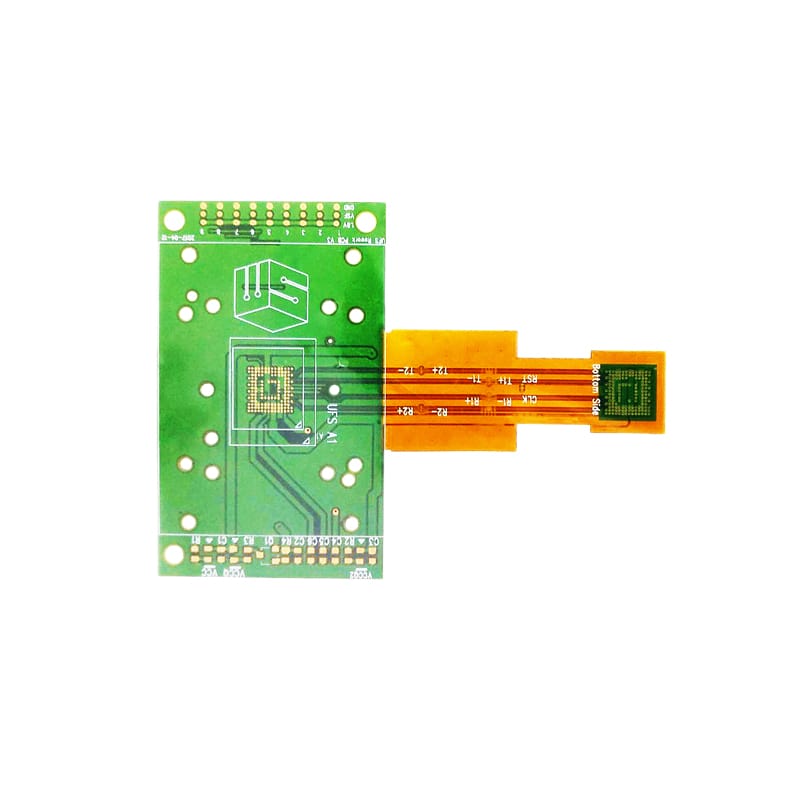

Starrflexible Leiterplatte

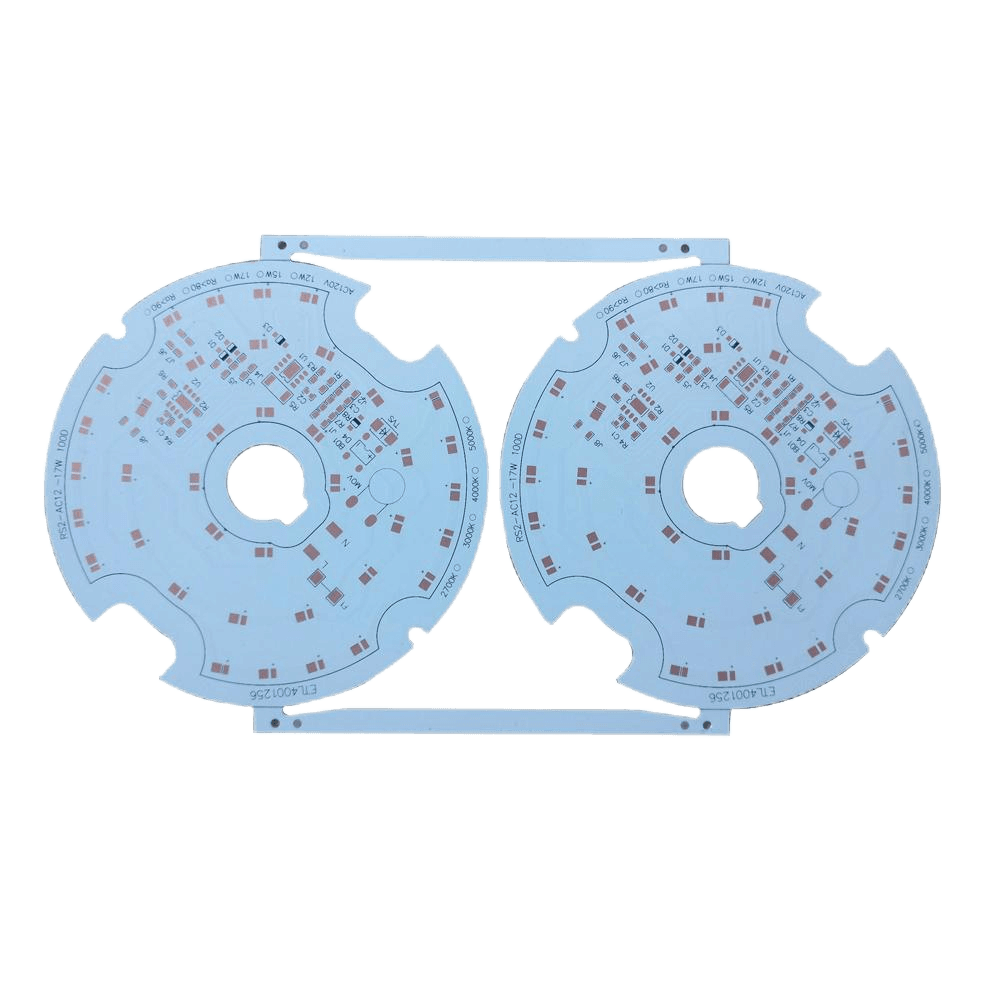

Aluminium-Leiterplatte

Leiterplatte mit hohem Kupfergehalt

HDI-Leiterplatte

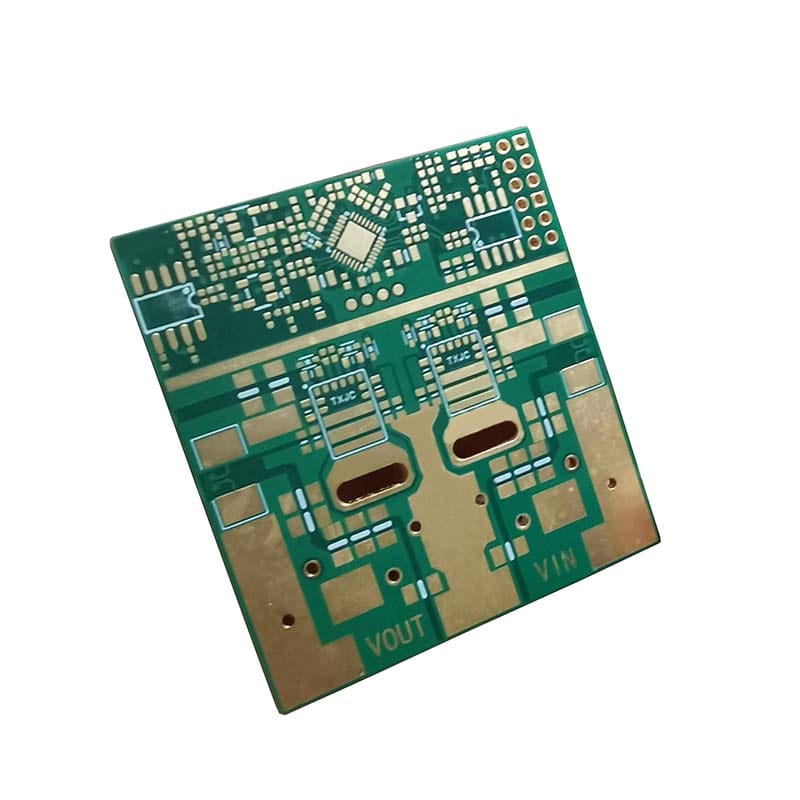

Hochfrequenz-Leiterplatte

PCB-Funktionen

Fertigungsmöglichkeiten für starre Leiterplatten

| Merkmale | Fähigkeit | Beschreibung |

| Schicht | 2/4/6/8/10/12/14/16/18/20.../32 Lagen PCB | Die Anzahl der Kupferschichten in der Leiterplatte |

| Impedanztoleranz | ±10% | |

| Material | FR-4 | |

| Aluminium-Kern | Einlagige Leiterplatte mit Aluminiumkern | |

| Kupferkern | Einlagige Leiterplatte mit Kupferkern und direkten Kühlkörperkontakten zum Kern (≥1 x 1 mm) | |

| HF-Leiterplatte | 10z Kupfer, 2-lagige HF-Leiterplatte mit Rogers- und PTFE-Kern | |

| Dielektrizitätskonstanten von FR-4 | 4,5 (2-lagige Leiterplatte) | 7628 Prepreg 4,4 3313 Perpreg 4,1 2116 Perpreg 4,16 |

| Max. Boardabmessungen | FR4-Leiterplatte: 600 × 600 mm Rogers/PTFE-Teflon-Leiterplatte: 550 × 400 mm Aluminium-Leiterplatte: 600 × 500 mm Kupfer-Leiterplatte: 480 × 280 mm | Diese Grenzwerte gelten für Leiterplatten mit einer Dicke von ≥0,8 mm. Die dünneren FR4-Leiterplatten sind maximal 500 x 600 mm groß. 2-lagige FR4-Leiterplatten können eine maximale Größe von 1000 x 660 mm erreichen. |

| Min. Board-Abmessungen | Normal: 3 × 3 mm. Zinnen-/Plattierte Kanten: 10 × 10 mm. | Diese Grenzwerte gelten für Leiterplatten mit einer Dicke von ≥0,6 mm. Bei dünneren Leiterplatten ist eine manuelle Überprüfung erforderlich. Für kleine Leiterplatten wird eine Panelisierung empfohlen. |

| Maßtoleranz | ±0,1 mm | ±0,1 mm (Präzision) und ±0,2 mm (Normal) für CNC-Fräsen und ±0,4 mm für V-Cut |

| Dicke | 0,4–4,5 mm | Die Dicke für FR4 beträgt: 0,4/D.6/0,8/1.DV1,2/1,6/2,0 mm (2,5 mm und mehr gelten nur für Leiterplatten mit 12+ Lagen) |

| Dickentoleranz (Dicke ≥ 1,0 mm) | ±10% | Beispielsweise beträgt die Dicke der fertigen Platte bei einer Plattendicke von 1,6 mm 1,44 mm (T-1,6 × 10%) bis 1,76 mm (T+1,6 × 10%). |

| Dickentoleranz (Dicke < 1,0 mm) | ±0,1 mm | Beispielsweise liegt die fertige Plattendicke bei einer Plattendicke von D.8 mm zwischen 0,7 mm (T-0,1) und 0,9 mm (T+0,1). |

| Fertige äußere Kupferschicht | 1 oz/2 oz (35 um/70 um) | Das fertige Kupfergewicht der Außenschicht beträgt 1 oz oder 2 oz. (Ohne die schwere Kupferplatine) |

| Fertige innere Kupferschicht | 0,5 Unzen/1 Unze/2 Unzen (17,5 um/35 uml 70 um) | Das fertige Kupfergewicht der inneren Schicht beträgt standardmäßig 0,5 oz. |

| Lötstoppmaske | Farben: Grün, Lila, Rot, Gelb, Blau, Weiß und Schwarz. | |

| Oberflächenbeschaffenheit | HASL (bleihaltig/bleifrei), ENIG, OSP (nur Kupferkernplatinen) | FR4-Leiterplatten sind in allen drei Ausführungen erhältlich, 6+Lagen und HF-Platinen haben nur ENIG. Leiterplatten mit Aluminiumkern haben nur HASL. Leiterplatten mit Kupferkern haben nur OSP. |

Bohren

| Merkmale | Fähigkeit | Beschreibung |

| Bohrdurchmesser | 1-lagig: 0,3–6,3 mm 2-lagig: 0,15–6,3 mm Mehrlagig: 0,15–6,3 mm | Löcher mit einem Durchmesser ≥ 6,3 mm werden aus einem kleineren Bohrloch CNC-gefräst. Der Mindestbohrdurchmesser für 2- oder mehrlagige Leiterplatten beträgt 0,15 mm (teurer). Der Mindestbohrdurchmesser für Leiterplatten mit Aluminiumkern beträgt 0,65 mm. Der Mindestbohrdurchmesser für Leiterplatten mit Kupferkern beträgt 1,0 mm. |

| Toleranz der Lochgröße (beschichtet) | Durchgangslöcher: +0,13/-0,008 mm Presspassungslöcher: ±0,05 mm (nur mehrschichtige ENIG-Platinen – geben Sie die spezifischen Löcher in der PCB-Anmerkung an) | Beispielsweise ist bei einer Lochgröße von 0,6 mm eine fertige Lochgröße zwischen 0,52 mm und 0,73 mm akzeptabel. |

| Toleranz der Lochgröße (nicht beschichtet) | ±0,2 mm | Beispielsweise ist für das nicht beschichtete Loch von 1,00 mm eine fertige Lochgröße zwischen 0,80 mm und 1,20 mm akzeptabel. |

| Durchschnittliche Lochbeschichtungsdicke | 18 μm | |

| Blinde/vergrabene Vias | unterstützt | |

| Min. Durchgangslochgröße/-durchmesser | 0,15 mm/0,25 mm | 1-lagig (nur NPTH): 0,3 mm Lochgröße/0,5 mm Durchgangsdurchmesser 2-lagig: 0,15 mm Lochgröße/0,25 mm Durchgangsdurchmesser Mehrlagig: 0,15 mm Lochgröße/0,25 mm Durchgangsdurchmesser |

| Min. nicht plattierte Löcher | 0,50 mm | Bitte zeichnen Sie NPTHs in die mechanische Ebene oder die Sperrebene. |

| Min. Plattierte Schlitze | 0,5 mm | Die minimale plattierte Schlitzbreite beträgt 0,5 mm und wird mit einem Pad gezogen. |

| Min. nicht plattierte Schlitze | 1,0 mm | Die minimale Breite des nicht plattierten Schlitzes beträgt 1,0 mm. Bitte zeichnen Sie den Schlitzumriss in die mechanische Schicht (GM1 oder GKO). |

| Abstand zwischen den Durchkontaktierungen | 0,2 mm | |

| Pad-Loch-zu-Loch-Abstand | 0,45 mm | |

| Min. Zinnenlöcher | 0,5 mm | Zinnenförmige Löcher sind metallisierte Halblöcher an den Kanten von Leiterplatten, die üblicherweise auf Tochterplatinen verwendet werden, die auf Trägerplatinen gelötet werden. ①Lochdurchmesser (Φ): ≥0,5 mm ②Loch zu Platinenrand (L): ≥1 mm ③Loch zu Loch (D): ≥0,5 mm ④Min. Leiterplattengröße: 10×10 mm ⑤Min. Leiterplattendicke: 0,6 mm |

| Beschichtete Kanten | 10 x 10 mm | Die plattierten Kanten sind verkupfert und ENIG-behandelt. HASL wird nicht unterstützt. ①Mindestgröße der Leiterplatte: 10 × 10 mm ②Mindestdicke der Leiterplatte: 0,6 mm ③Mindestens 3 Unterbrechungen (bei größeren Leiterplatten mehr) in der Kantenplattierung sind für die Verbindungen der Stützlaschen erforderlich |

| Blind Slot | ①Breite des Blindschlitzes (W): ≥1,0 mm ②Tiefe des Blindschlitzes (D): ≥0,2 mm ③Ringweite des Blindschlitzes (A): ≥0,3 mm (Padbreite der PTH-Blindschlitze) ④Sicherheitsabstand (S): ≥0,2 mm (Abstand von NPTH-Blindschlitzen zu Pad/Leiterbahnen/Kupferfläche) ⑤Verbleibende Dicke des Blindschlitzes (R): ≥0,2 mm (Abstand vom Boden des Blindschlitzes zur nächstgelegenen inneren Kupferschicht/Oberflächensubstrat) ⑥Unterstützt 2–32-lagige FR4-Platinen mit einer Dicke von ≥0,8 mm |

Spuren

| Merkmale | Fähigkeit | Beschreibung |

| Min. Spurbreite und -abstand (1 oz) | 0,10/0,10 mm (4/4mil) | Ein- und zweischichtig: 0,10/0,10 mm (4/4 mil). Mehrschichtig: 0,09/0,09 mm (3,5/3,5 mil). 3 mil ist in BGA-Fan-Outs akzeptabel. |

| Min. Spurbreite und -abstand (2 oz) | 0,16/0,16 mm (6,5/6,5 mil) | 2-lagig: 0,16/0,16 mm (6,5/6,5 mil) Mehrschichtig: 0,16/0,20 mm (6,5/8 mil) |

| Spurbreitentoleranz | 20% | Beispielsweise liegt die fertige Spurbreite bei einer 0,1 mm dicken Spur zwischen 0,08 und 0,12 mm. |

| PTH-Ring | ≥0,2Dmm | Doppelschicht: 1 oz: Empfohlen 0,25 mm oder mehr; absolutes Minimum 0,18 mm 2 oz: 0,254 mm oder mehr Mehrschicht: 1 oz: Empfohlen 0,20 mm oder mehr; absolutes Minimum 0,15 mm 2 oz: 0,254 mm oder mehr |

| NPTH-Pad-Ring | ≥0,45 mm | Empfohlen werden 0,45 mm oder mehr. Dadurch kann ein 0,2 mm dicker Kupferring um das Loch herum entfernt werden, damit die Dichtungsfolie befestigt werden kann. Padgrößen, die kleiner als der empfohlene Wert sind, können dazu führen, dass der Ring sehr dünn ist oder ganz fehlt. |

| Ball Grid Array | 0,25 mm | ①BGA-Pad-Durchmesser ≥0,25 mm ②BGA-Pad-zu-Leiterbahn-Abstand ≥0,1 mm (min. 0,09 mm für Mehrschichtplatinen) ③Vias können innerhalb der BGA-Pads platziert werden, indem gefüllte und überplattierte Vias verwendet werden |

| Spurspulen | 0,15/0,15 mm | Minimale Leiterbahnbreite/-abstand: 0,15/0,15 mm, wenn die Leiterbahnen mit Lötstopplack (1 oz) abgedeckt sind. Minimale Leiterbahnbreite/-abstand: 0,25/0,25 mm, wenn die Leiterbahnen NICHT mit Lötstopplack (1 oz) abgedeckt sind. Nur ENIG (hohes Kurzschlussrisiko mit HASL) |

| Schraffierte Rasterbreite und -abstand | 0,25 mm | |

| Gleicher Netzspurabstand | 0,25 mm | |

| Abstand zwischen Durchgangsloch und Kupfer in der inneren Schicht | 0,2 mm | |

| Abstand zwischen Loch des PTH-Pads in der Innenschicht und Kupfer | 0,3 mm | |

| Abstand zwischen Unterlage und Schiene | 0,1 mm | Min. 0,1 mm (wenn möglich deutlich darüber bleiben). Min. 0,09 mm lokal für BGA-Pads |

| SMD-Pad-zu-Pad-Abstand (verschiedene Netze) | 0,15 mm | Weitere Details zum SMD-Pad-Abstand: SMD-Komponenten Mindestabstand |

| Durchkontaktierung zur Schiene | 0,2 mm | |

| PTH zum Tracken | 0,28 mm | 0,35 mm werden empfohlen, mindestens 0,28 mm |

| NPTH zum Verfolgen | 0,2 mm |

Flexible PCB-Fertigungsmöglichkeiten

| Merkmale | Beschreibung | Fähigkeit |

| Schicht | Eine Schicht, zwei Schichten | Die Anzahl der Kupferschichten im FPC |

| FPC-Stapelung | Einseitig | FPC mit Kupfer und Deckschicht nur auf derselben Seite. Innere PI-Dicke: 25 μm |

| Doppelseitig | FPC mit Kupfer auf beiden Seiten. Innere PI-Dicke: 25 μm | |

| Maße | Maximale Abmessungen | Normal: 234 × 490 mm |

| Mindestabmessungen | Keine Begrenzung, aber die Gesamtabmessung kleiner als 20×20mm ist die beste Plattengröße | |

| FPC-Fertigdicke | Einseitig: 0,07/0,11 mm Doppelseitig: 0,11/0,12/0,2 mm | |

| Kupfergewicht der äußeren Schicht | Einseitig 18 μm (0,5 oz), 35 μm (1 oz) Doppelseitig: 12 μm (0,33 oz), 18 μm (0,50 oz), 35 μm (1 oz) | |

| Art des Prozesses | Trockenfilmverfahren mit LDI-Belichtungstechnologie (Laser Direct Image) | |

| Oberflächenbeschaffenheit | ENIG-Dicke: 1u"/2u" | |

| Dicke mit Versteifung | Dicke mit Versteifung ist FPC-Dicke + Versteifungsdicke | |

| FPC-Dickentoleranz | ±0,05 mm | |

| Löcher | Lochdurchmesser | 0,15–6,5 mm |

| Durchmessertoleranz | ±0,08 mm | |

| Minimaler plattierter Schlitz | 0,50 mm | |

| Minimaler nicht plattierter Schlitz | Nicht begrenzt | |

| Zinnenlöcher | Zinnenlöcher sind plattierte Halblöcher am Rand einer flexiblen Leiterplatte (FPC). Sie werden am häufigsten für pressgelötete Steckverbinder verwendet. ① Durchmesser des Zinnenlochs: ≥0,3 mm ② Abstand zwischen Zinnenloch und Platinenrand: ≥0,5 mm ③ Abstand zwischen Zinnenloch und Loch: ≥0,4 mm | |

| Min. Durchgangslochgröße/-durchmesser | 0,15 mm (Durchgangslochgröße)/0,35 mm (Durchgangsdurchmesser) ①Ring: mindestens 0,1 mm, 0,125 mm empfohlen ②Empfohlene Durchgangslochgröße: 0,3 mm innen, 0,55 mm außen | |

| Spuren | Ring für PTH | ≥0,25 mm empfohlen, absolute Grenze 0,18 mm |

| Minimale Leiterbahnbreite/-abstand (1oz) | 12 μm (0,33 oz) Kupfer: 3/3 mil (absolute Grenze 2/2 mil) 18 μm (0,5 oz) Kupfer: 3,5/3,5 mil 35 μm (1 oz) Kupfer: 4/4 mil Dies sind Standardfunktionen. Kontaktieren Sie den Kundendienst für individuelle Anforderungen. | |

| Toleranz der Leiterbahnbreite | ±20% | |

| Abstand zwischen Pad und Leiterbahn | ①Via-Ring zur Spur: ≥0,1 mm ②Freiliegendes Pad zur Spur: ≥0,15 mm | |

| NPTH zur Kupferfreigabe | ≥0,20 mm | |

| Ball Grid Array | ①BGA-Pad-Durchmesser: ≥0,25 mm ②BGA-Pad-zu-Leiterbahn-Abstand: ≥0,2 mm | |

| Deckschicht/ Lötstoppmaske | Deckfarbe | Gelb/Schwarz/Weiß |

| Coverlay-Öffnung | Decklagenausdehnung (einseitig): 0,1 mm Decklagenöffnung zum Leiterbahnabstand: ≥0,15 mm | |

| Ma bedeckt | Es wird empfohlen, die Deckschicht über den Durchkontaktierungen zu belassen | |

| Deckschichtdicke | ①PI: 12,5 μm, Kleber: 15 μm (auf 12/18 μm Kupfer) ②PI: 25 μm, Kleber: 25 μm (auf 35 μm Kupfer) | |

| Minimale Lötbrückenbreite | Mindestens 0,5 mm, d. h. Lötbrücken, die schmaler als 0,5 mm sind, werden entfernt. Bei abweichenden Anforderungen wenden Sie sich bitte an den Kundendienst. | |

| Siebdruck | Zeichenhöhe | ≥1 mm (mehr bei komplexen Mustern oder Knock-Out-Text) |

| Zeichenlinienbreite | ≥0,15 mm (schmalere Linien lassen sich nicht gut drucken) | |

| Abstand zwischen Zeichen und Pad | ≥0,15 mm (Jeder Siebdruck, der näher an einem Pad liegt, wird abgeschnitten) | |

| FPC-Gliederung | Laserumriss | ①Kupfer bis zur Platinenkante ≥0,3 mm ②Kupfer bis zu den Schlitzen ≥0,3 mm ③Umrisstoleranz: ±0,1 mm (±0,05 mm auf Anfrage) |

| Abstand zwischen goldenem Fingerpad und Platinenkante | 0,2 mm. Goldkontakte werden bei Überschreitung dieses Abstands gekürzt, um Beschädigungen beim Laserschneiden der Kontur zu vermeiden. Zinnenförmige Pads sind von diesem Abstand ausgenommen. | |

| Panels (siehe FPC-Panel-Designhandbuch) | ①Der Abstand zwischen den Platten beträgt üblicherweise 2 mm. Für Platten mit Metallversteifungen sollten Sie stattdessen 3 mm verwenden. ②An allen vier Seiten sind 5 mm breite Bearbeitungskanten erforderlich. An diesen Kanten ist Kupferguss erforderlich, mit 1 mm Abstand um die Passmarken und 0,5 mm Abstand um die Werkzeuglöcher. ③Passmarken: 1 mm; Werkzeuglöcher: 2 mm; Mitte der Passmarke zur Plattenkante: 3,85 mm. Fügen Sie vier Passmarken hinzu, wobei eine um 5 mm oder mehr versetzt sein muss. ④Breite der Stützlaschen: 0,7–1,0 mm ⑤Maximale Plattengröße: 230 × 480 mm | |

| FPC-Versteifungen | PI-Versteifung | Dickenoptionen: 0,1 mm, 0,15 mm, 0,20 mm, 0,225 mm, 0,25 mm |

| FR4-Versteifung | Dickenoptionen: 0,1 mm, 0,2 mm | |

| Edelstahlversteifung | Dickenoptionen: 0,1 mm, 0,2 mm, 0,3 mm | |

| 3M Klebeband | 3M9077 (0,05 mm dick, hitzebeständig) 3M468 (0,13 mm dick, nicht hitzebeständig) | |

| EM-Abschirmfolie | 18 μm dick, schwarz. Hilft, die elektromagnetische Verträglichkeit zu senken. Es wird empfohlen, Lötmaskenöffnungen über den Kantenschutzschienen hinzuzufügen, um sie elektrisch mit den Abschirmfolien zu verbinden. | |

| Überlegungen zum Entwurf | Impedanzberechnung | Kern Polyimid er.3.3 Deckschicht er.2.9 Kern Polyimid Dicke: 25 μm |

| Andere Designbeschränkungen | Dieselben Anforderungen wie bei starren Leiterplatten hinsichtlich Löchern, Leiterbahnen, Lötstoppmaske und Siebdruck. |

FAQs

Ein PCB-Schaltplan ist die visuelle Darstellung einer elektronischen Schaltung. Er zeigt, wie Komponenten wie Widerstände, Kondensatoren und ICs zu einer Schaltung verbunden sind. Er dient als Vorlage für das PCB-Layout und unterstützt Ingenieure während des Herstellungsprozesses.

Der PCB-Stackup beschreibt die Anordnung von Kupferschichten und Isoliermaterialien auf einer Leiterplatte. Er definiert die Struktur der Signal-, Strom- und Masseschichten und beeinflusst die Leistung, die elektromagnetische Störung und die Herstellbarkeit der Leiterplatte – insbesondere bei mehrschichtigen Leiterplatten.

HASL (Hot Air Solder Leveling): Eine kostengünstige Oberflächenveredelung für Leiterplatten mit geschmolzenem Lot. Sie eignet sich für größere Bauteile, ist jedoch nicht ideal für Fine-Pitch- oder High-Density-Leiterplatten. ENIG (Electroless Nickel Immersion Gold): Eine flache, glatte und äußerst zuverlässige Oberfläche, ideal für Fine-Pitch-, BGA- und High-End-Leiterplatten. Bietet bessere Korrosionsbeständigkeit und längere Haltbarkeit.

1.Automatische optische Inspektion (AOI) – Prüft mit Kameras auf Oberflächendefekte. 2.In-Circuit-Test (ICT) – Prüft die elektrische Leistung der Komponenten auf der Platine. 3.Flying-Probe-Test – Verwendet bewegliche Sonden, um Punkte auf Platinen mit geringem bis mittlerem Volumen zu testen. 4.Funktionstest (FCT) – Simuliert den realen Betrieb, um die volle Funktionalität zu überprüfen. 5.Röntgeninspektion (AXI) – Prüft versteckte Lötstellen (wie BGA) und innere Schichten. 6.Burn-In-Test – Belastet die Leiterplatte, um frühzeitige Ausfälle zu identifizieren. 7.Sichtprüfung – Manuelle Prüfung auf Oberflächendefekte, oft ein letzter Qualitätsschritt.